Article published on magnetic domain wall logic gates

A new logic-in-memory architecture based on chirally-coupled domain wall inverters and spin-orbit torques allows for designing magnetic logic gates that provide nonvolatile data retention and scalability beyond CMOS logic.

Over the past decades, computers have become indispensable in our daily lives. In conventional computers, computation and data storage are physically separated, which is commonly referred to as a von Neumann architecture. However, von Neumann computers will ultimately fail to meet the increasing demand for the emerging applications such as the internet of things (IoT), which require ultra-low power consumption, a compact architecture, as well as big data, which requires frequent access to vast amounts of data.

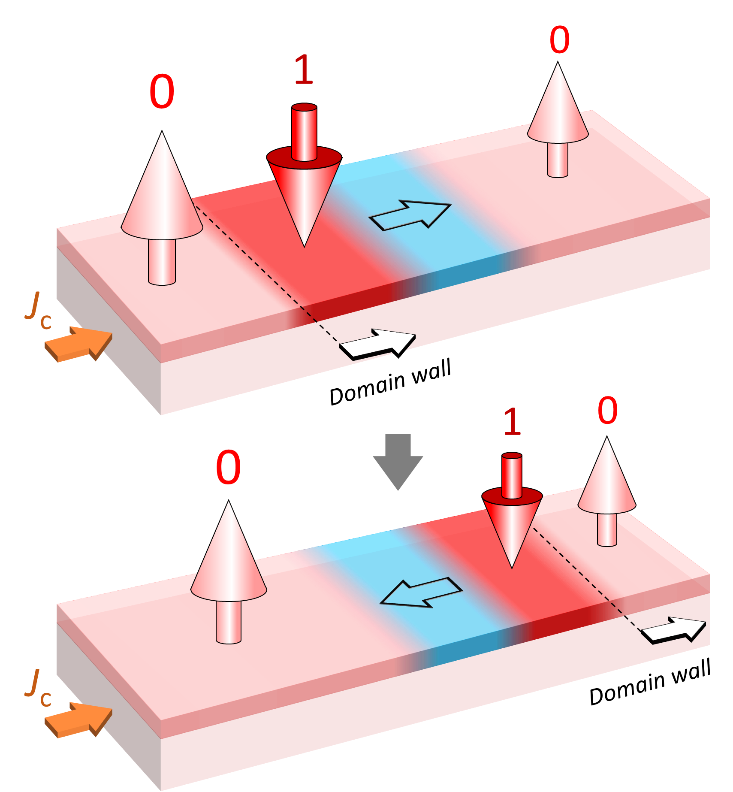

In order to meet these requirements, scientists are looking beyond conventional electronic circuits and transistors, which are based on the control of the electron charge, and have turned instead to its spin. The electron spin, due to its quantum properties, can only point up or point down. This is an ideal property for digital data where spin up and spin down can represent 1’s and 0’s. Indeed, magnets, the collective manifestation of the electron spin, have been used as storage bits in magnetic hard disc drives (HDDs) since the 1950s. Despite the extensive industrial use of magnets for data storage, one of the key challenges is to build a microprocessor using spin-based logic devices. Such devices would combine the best of two worlds, namely the data processing capability of transistors with the non-volatile memory of magnets, thus eliminating the need for energy-hungry data refresh processes. In 2002, Allwood et al. proposed the idea of magnetic domain-wall logic with logic operations performed by driving domain walls with a magnetic field through nanoscale wires in a tailor-made device. Magnetic domain walls are small regions separating magnetic domains with different magnetization. In 2008, scientists from IBM developed the concept of racetrack memory where the magnetic domain walls are shifted along a nanowire using an electric current, making a high-density, high-speed, and non-volatile data storage device possible. This stimulated a great deal of work to improve the domain wall speed and efficiency. Nevertheless, the realization of electrically controlled magnetic domain-wall logic devices remained to be achieved.

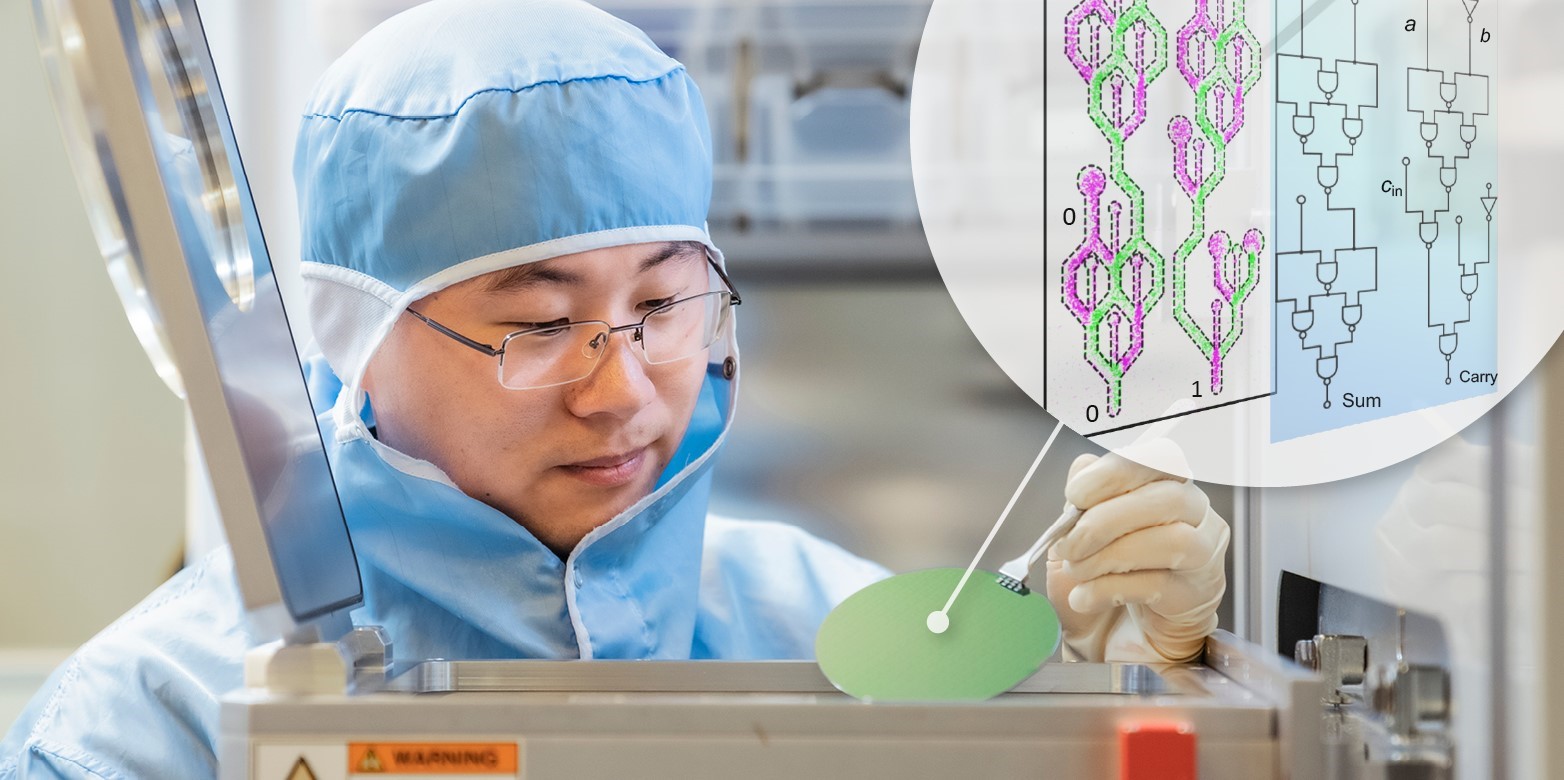

Recently, scientists from ETH Zurich and Paul Scherrer Institute have created an all-electric logic device based on magnetic domain walls in racetracks using a very effective type of magnetic coupling, called “lateral chiral coupling”, which they first demonstrated in 2019. Here, adjacent magnetic domains with out-of-plane and in-plane magnetizations are coupled with a fixed chirality via the interfacial Dzyaloshinskii-Moriya interaction (DMI), which was proposed by the scientists Dzyaloshinskii and Moriya 60 years ago. Exploiting this chiral coupling, Luo and his colleagues first created the essential building block for these devices - a magnetic domain wall inverter (Fig. 1). When passing through the inverter, an up|down (↑|↓) domain wall transforms into a ↓|↑ DW and vice versa. This inverter is equivalent to a NOT gate in the Boolean logic with the binary data encoded into the magnetization of the moving domains, i.e ↑ =”0” and ↓="1".

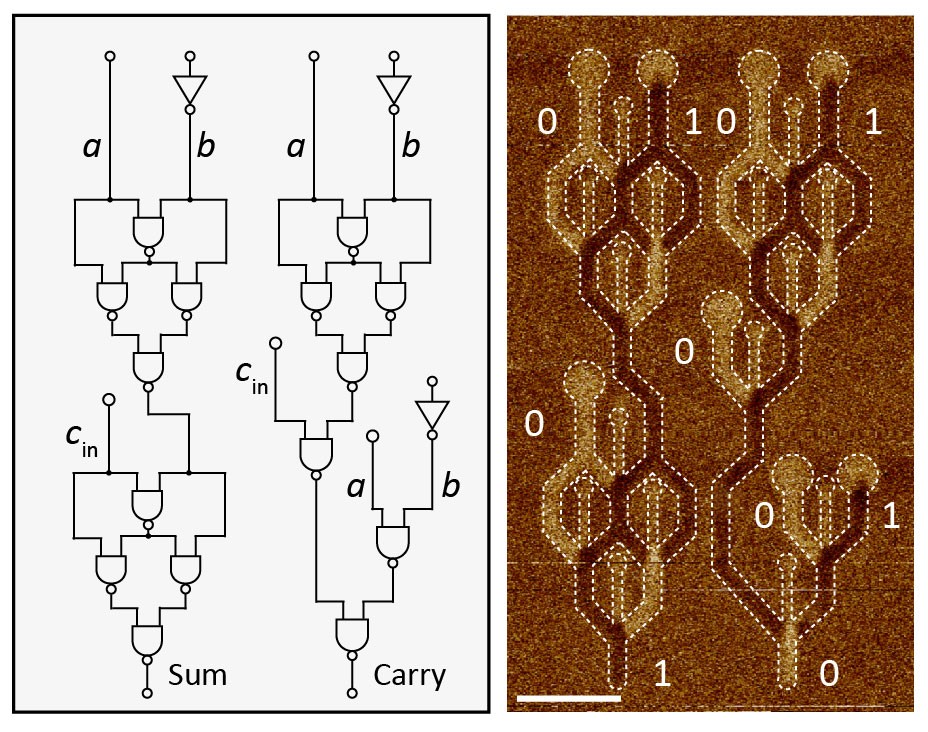

Using a similar principle, they further realized a NAND gate, which is a universal gate, so that any other logic operation can achieved with a combination of several NAND gates. They also demonstrated the complete set of logic functions, creating a NOT gate, a NAND gate, a cross-over, a switch, and a fan-out device. Finally, they combined as many as 15 NAND gates in a single racetrack circuit and demonstrated the function of a full adder (a logic circuit that takes two numbers as an input and outputs their sum) by applying an electric current, which is one of the key functions in a microprocessor (Fig. 2).

In summary, there are a number of key features that make this DW logic device special. The computation is closely associated with the non-volatile racetrack memory. Specifically, this is a logic-in-memory architecture that can go beyond the so-called von Neumann bottleneck and reduce the energy used and time needed for the transfer of data between computation and storage units. With this, it becomes possible to create an ultra-low-power and compact chip, which could perform as both computation and memory. In addition, unlike the CMOS logic where an elementary NAND gate is composed of four transistors and has a complex physical layout, a domain wall NAND gate can be created in a straightforward manner by physically connecting two magnetic racetracks. Furthermore, we can adopt the standard nanofabrication processes used for Silicon CMOS fabrication to create large-scale domain-wall logic circuits.

Of course, there are still many challenges before bringing a magnetic domain wall microprocessor into commercial production. One issue is how to write and read the magnetic domains when the structure is made small enough to fulfill the requirement to have a high-density of devices. It turns out that there are scientists at the Interuniversity Microelectronics Centre (IMEC) in Belgium who are developing a so-called magnetic tunnel junction (MTJ)/racetrack hybrid architecture, which would provide electric access to nanomagnetic domains on the racetracks. "We will adopt this technology to further develop our logic device into an industry-ready product as a commercial spin microprocessor." says Zhaochu Luo, physicist at ETH Zurich and Paul Scherrer Institute.

Selected publications:

Current-driven magnetic domain-wall logic

Z. Luo, A. Hrabec, T. P. Dao, G. Sala, S. Finizio, J. Feng, S. Mayr, J. Raabe, P. Gambardella, L. J. Heyderman

external page Nature 579, 214 (2020)

Chiral domain wall injector driven by spin-orbit torques

T. P. Dao, M. Müller, Z. Luo, M. Baumgartner, A. Hrabec, L. J. Heyderman, P. Gambardella

external page Nano Lett. 19, 5930 (2019)

Chirally Coupled Nanomagnets

Z. Luo, T. P. Dao, A. Hrabec, J. Vijayakumar, A. Kleibert, M. Baumgartner, E. Kirk, J. Cui, T. Savchenko, G. Krishnaswamy, L. J. Heyderman, P. Gambardella

external page Science 363, 1435 (2019)

Patents:

Current-driven magnetic domain wall logic

Z. Luo, A. Hrabec, P. Dao, L.J. Heyderman, P. Gambardella

European Patent application EP20161352.8 (2020)